Съдържание

- История на поколенията микропроцесори

- Основни етапи в разработването на Intel Celeron и Pentium

- Проектиране на централен процесор

- Видове микросистеми

- Еволюцията на Intel x86

- 80286: 16-битов микропроцесор

- 80486: технология за кеширане

- База за устройства 486

- Блокове RISC

- Архитектура CISC

- Предимства и недостатъци

Микропроцесорът се състои от няколко блока, свързани помежду си, като всеки блок изпълнява определена функция. Проектирането и взаимовръзката на тези блокове се нарича архитектура. Скоростта, с която компютърът може да чете инструкции и да извършва съответните изчисления, се определя от работната честота на микропроцесора. Производителите са постигнали голям напредък в разработването на архитектури, които позволяват на компютрите да стават все по-малко зависими от честотата, което означава, че микропроцесорите с по-ниски честоти и скорости могат да извършват повече изчисления и задачи. Еволюцията на микропроцесорната архитектура премина от едноядрена към многоядрена архитектура, способна да обработва множество части от информацията едновременно.

История на поколенията микропроцесори

Fairchild Semiconductor (Феърчайлд полупроводник), основана през 1957 г., изобретява първата си интегрална схема през 1959 г., която поставя началото на историята на микропроцесорите. През 1968 г. Джордан Мур, Робърт Нойс и Андрю Гроув напускат Junior Semiconductor Fair и основават своя собствена компания: Integrated Electronics (Intel). През 1971 г. компанията изобретява първия компютър Intel 4004.

Днес съществуват няколко поколения микропроцесорни архитектури:

- 1-во поколение от 1971 до 1973 г. 1971 INTEL 4004 с тактова честота 108 kHz. През този период на пазара се използват и други модели, включително Rockwell International PPS-4, INTEL-8008 и National semiconductors IMP-16, които не са TTL съвместими устройства.

- Второ поколение - от 1973 до 1978 г. се прилагат много ефективни 8-битови микропроцесори като Motorola 6800 и 6801, INTEL-8085 и Zilogs-Z80. Заради свръхвисоките си скорости те бяха скъпи, тъй като се основаваха на производството на NMOS, но въпреки цената бяха много популярни.

- Микропроцесорната архитектура от трето поколение се използва от 1979 до 1980 г.През този период са разработени INTEL 8086/80186/80286 и Motorola 68000 и 68010. Скоростите на тези процесори са четири пъти по-високи от тези на техните предшественици.

- Четвърто поколение от 1981 до 1995 г. - разработени са 32-битови микропроцесори, използващи HCMOS. INTEL-80386 и Motorola 68020/68030 бяха популярни процесори.

- Петото поколение започва през 1995 г. и продължава да се развива. През този период на пазара беше представена 64-битова модерна микропроцесорна архитектура, която включва Pentium, Celeron, Dual и Quad Core.

Основни етапи в разработването на Intel Celeron и Pentium

Intel Celeron е представен през април 1998 г. и принадлежи към фамилията процесори Intel X86 за персонални компютри. Базиран на Pentium 2 и способен да изпълнява всички компютърни програми IA-32.

История на Intel Celeron:

- 4 /01/2000 - Intel Celeron 533.0 MHz;

- 14/02/2000 - Intel Celeron 450/500 MHz mobile;

- 19/06/2000 - мобилен Intel Celeron с ниско напрежение, 500.0 MHz;

- 3/01/2001 - Intel Celeron, 800 MHz;

- 2001 г. - Intel Celeron (1,2 GHz)

- 2002 г. - Микропроцесорна архитектура Intel Celeron (1.3, 2.10, 2.20GHz);

- 2003 г. - Мобилен процесор Intel Celeron 2/ 2.55 GHz.

- 2004 г. - Intel Celeron M 320 и 310 (1,3, 1,2 GHz);

- 2008 - Celeron Core 2 DUO (Allendale).

Pentium е представен на 2 март 1993 г. Той замени микропроцесорната архитектура Intel 486, като числото 4 означава четвъртото поколение микроархитектура в историята на микропроцесорите. Pentium се отнася за едноядрения x 86 на Intel, който се основава на архитектура от пето поколение. Името на този процесор произлиза от гръцката дума penta, която означава "пет".

Оригиналният процесор Pentium е заменен от Pentium MMX през 1996 г. и има 64-битова шина за данни. Стандартен единичен цикъл на трансфер може да чете или записва до 64 бита едновременно. Циклите Burst за четене и запис се поддържат от процесорите Pentium. Те се използват за операции с кеша и прехвърлят 32 байта (размер на линията на кеша на Pentium) за 4 такта. Всички операции с кеша са пакетни цикли за.

Проектиране на централен процесор

Архитектурата на микропроцесора има много периферни устройства, произведени на един чип. Имаше ALU (аритметичен логически блок), блок за управление, регистри, шини и часовник за изпълнение на изчислителни задачи.

Микропроцесорът е пакет с един чип, в който са интегрирани редица полезни функции и е направен на един силициев полупроводников чип. Архитектурата му се състои от процесор, модули памет, системна шина и входно-изходен модул. Системната шина свързва различните блокове, за да улесни обмена на информация. Освен това той се състои от шини за данни, адреси и управление за правилен обмен на данни, което е свързано с основната концепция за архитектура на микропроцесора.

Процесорът се състои от един или няколко аритметични логически блока (ALU), регистри и блок за управление. Въз основа на регистрите е възможно да се класифицира и броят на поколенията. ALU изчислява всички аритметични и логически операции с данни и определя размера на микропроцесора, напр. 16- или 32-битов.

Блокът памет съдържа програмата и данните и е разделен на процесорна, първична и вторична памет. Блокът за вход и изход свързва подобни периферни комуникационни устройства с микропроцесора, за да получава и изпраща информация.

Видове микросистеми

Съществуват няколко вида архитектура на микропроцесорите, които се използват в различни системи:

- Съпроцесори. Това е допълнителен микропроцесор, който работи заедно с основния микропроцесор. Той е проектиран и оптимизиран да се използва за конкретна задача и увеличава скоростта на обработка чрез едновременната работа на основния процесор. Пример за това е математически копроцесор или ускорител с плаваща запетая.

- Скаларният процесор извършва изчисления за едно число или набор от данни в даден момент; той се среща в повечето съвременни компютри и е известен като процесор с един поток инструкции или, накратко, SISD.

- Архитектурата на процесорните масиви на съвременните микропроцесори, известна още като векторни масиви, позволява на една инструкция да работи едновременно в няколко точки с данни. Известен е като SIMD процесор с една команда за множество данни, широко използван в прогнозирането на времето и моделирането на въздушните потоци.

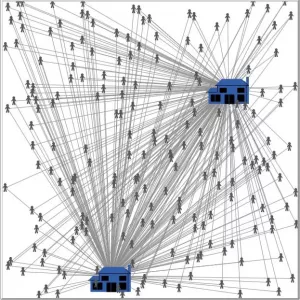

- Паралелният процесор използва независими микро да работи над същата програма. Разглежданият процес е разделен на задачи, всяка от които може да се обработва от. Всички те се координират от сложна операционна система. Програмите трябва да бъдат специално написани за паралелна обработка, в противен случай някои от тях няма да могат да приключат, докато другите не приключат, в зависимост от резултата на текущия процес.

Микропроцесорите се разделят на пет вида: CISC-комплексен набор инструкции, RISC микропроцесор с намален набор инструкции, специализирана интегрална схема ASIC, суперскаларни процесори и микропроцесори за цифров сигнал DSP.

Тези процесори се използват за кодиране и декодиране на видео или за преобразуване на DAC (цифрово-аналогов) и A/D (аналогово-цифров). Искат микропроцесор, който е отличен в математическите изчисления. Този процесорен чип се използва в RADAR, системи за домашно кино, SONAR, аудиосистеми, декодери и мобилни телефони.

Еволюцията на Intel x86

Архитектурата x86 на Intel се е развивала през годините. От 29 000 транзистора микропроцесори 8086 с четири ядра Процесор Intel Core 2 съдържа 820 милиона транзистора, така че организацията и производствена технология драстична промяна.

Някои от най-важните моменти в развитието на архитектурата x86:

- 8080 е първият в света микропроцесор с общо предназначение. Има микропроцесорна архитектура на паметта с 8-битов път на трансфер данни в паметта. Използван е в първия персонален компютър.

- 8086 е 16-битова машина, много по-мощна от своя предшественик, има реален режим и 1 МВ адресируема памет. Той има по-широк път за данни: 16-битови и по-големи регистри, както и кеш или опашка от команди, които са били избрани преди изпълнението.

- 80286 - има 16MB адресируема памет и съдържа два режима: реален режим и 16-битов режим от първо поколение. Широчината на данните е 16 бита, а софтуерният модел също е 16-битов.

80286: 16-битов микропроцесор

По същество това е микропроцесор, разширена версия на 8086. Затова преди, как да разберем 80286, трябва да имате минимални познания за 8086. Intel 8086 е 16-битов микропроцесор, предназначен за използване като централен процесор в микрокомпютри. Терминът "16-битов" означава, че аритметичният логически блок, вътрешните регистри и инструкциите са проектирани да обработват 16-битови двоични кодове. Има 20-битова адресируема шина и 16-битова шина за данни. По този начин той може да получи достъп до всяко от 1048576 места в паметта и да чете или записва данни в паметта и портовете по 16 или 8 бита едновременно.

Архитектурата на микропроцесора 80286 е специално проектирана за многопотребителски и многозадачни. Той има четири нива на защита на паметта и поддържа операционна система. Той работи повече от два пъти по-бързо за един тактов цикъл в сравнение с предшествениците си Intel 8086/8088. Сложните математически операции отнемат по-малко тактови цикли от 8086. Той елиминира мултиплексирането на шината и има линейна адресна шина с 24 адресни линии, които могат директно да прехвърлят 16 MB памет. Това се поддържа от модул за управление на паметта и чрез него може да се заделя 1 GB памет, известна също като виртуална памет. Процесорът включва различни вградени механизми, които могат да защитават системния софтуер от потребителски програми и да ограничават достъпа до определени области на паметта.

Има два режима на работа за 80286. Режим на реален адрес и режим на защитен виртуален адрес. По принцип в този режим един потребител не пречи на друг. Те не могат да се намесват и в операционната система. Тези функции се наричат охранителни. 80286 съдържа четири блока за обработка:

- Единица автобус.

- Блок с инструкции.

- Блок за изпълнение.

- Блок с адреси.

Докато текущата инструкция се изпълнява, БУ предварително избира инструкция s и я съхранява в опашка от шест байта. Функцията U е да декодира усъвършенствани инструкции и да съхранява опашка от три декодирани инструкции. Адресният блок изчислява адреса на паметта или I/O устройствата, който трябва да бъде изпратен за операции за четене и запис. Всичките четири блока работят паралелно в процесора. Тази реализация на предсказване на преходи в микропроцесорната архитектура се нарича конвейер.

Следващата еволюционна посока е микропроцесорът 80386, първата 32-битова машина на Intel. Благодарение на своята архитектура той е в състояние да се конкурира със сложността и мощността на микрокомпютрите и мейнфреймите, въведени няколко години по-рано. Това беше първият процесор, който поддържаше многозадачна работа и съдържаше 32-битов защитен режим. Той прилага концепцията за размяна. Той има 4 GB адресируема физическа памет и 32-битова ширина на данните.

80486: технология за кеширане

По-късно в 1989 На пазара се появява Micro 80486, който въвежда концепцията за технология за кеширане и конвейерна обработка на инструкциите. Той съдържаше функция за защита от запис и предлагаше вграден математически копроцесор, който извършваше сложни операции от Основен процесор.

Разновидности на микро 4-то поколение:

- Pentium - използването на суперскаларни техники е въведено, когато няколко инструкции започват да се изпълняват паралелно. Добавена е функцията за разширяване на размера на страницата (PSE) като незначително подобрение в странирането на страници.

- Pentium Pro - използва преименуване на регистрите, предсказване на разклонения, анализ на потока от данни, спекулативно изпълнение и други стъпки на конвейера. Добавени са и усъвършенствани техники за оптимизация в микрокода и кеша от ниво 2. Той реализира преобразуване на адреси от второ поколение, което превръща 32-битов виртуален адрес в 36-битов физически адрес на паметта.

- Pentium II. Той е в състояние ефективно да обработва видео, аудио и графични данни, като използва фамилията микропроцесорни архитектури Intel MMX.

- Pentium III - съдържа SMD инструкции (разширения за стрийминг) и поддържа 3D графичен софтуер. Максималната тактова честота на процесора е 1,4 GHz и съдържа 70 нови инструкции.

- Pentium IV - реализира трето поколение преобразуване на адреси, което преобразува 48-битов виртуален адрес на паметта в 48-битов физически адрес на паметта. Той съдържа и други подобрения в работата с плаваща запетая за мултимедия.

- Core е първата микропроцесорна архитектура от фамилията двуядрени процесори на Intel, която представлява реализация на два процесора в един чип и разполага с допълнителна технология за рендиране.

- Core 2 разширява архитектурата си до 64-битова, а Core 2 Quad осигурява четири процесора в един чип. Наборът от регистри, както и режимите на адресиране са 64-битови. Той съдържа електронна схема от 1,2 милиона транзистора. Работната му честота за различните версии е 25, 33, 66 и 100 MHz. Това е от три до пет пъти по-бързо от 80386. По принцип чипът се предлага в две версии: DX и SX. DX-версията е 32-битов процесор, разположен в 168-изводна решетка, и може да работи с тактова честота между 25 и 66 MHz.

База за устройства 486

Понятието за архитектура, на което се разделят микропроцесорите, е сложно и включва елементи като блокова схема, контрол на достъпа, скорост на предаване на данни, формат на данните и прекъсвания.

Важни допълнителни характеристики на процесора 486 в сравнение с 386 са следните:

- Вграден математически копроцесор. В система 386 математиката се изпълнява на външно устройство, така че тези инструкции са три пъти по-бързи в система 486.

- 8 килобайта кеш за код и данни в чипа.

- Дизайн с висока надстройка.

- Изпълнителна единица.

- Блок за управление.

- Блок за интерфейс на шината.

- Единица за предварително извличане на код.

- Блок за декодиране на команди.

- Сегментиране на n-единици.

- Устройство за пейджинг.

- Блок на кеша.

- Единица с плаваща запетая.

- Блокът за предварително извличане на код съдържа опашка от 32 байта за съхранение блок за извличане на команден код.

- Блокът за управление съдържа и контролния ROM, в който се съхранява микрокодът. Адресът, зададен в програмата, се нарича логически адрес. Освен това осигурява 4 нива на защита, за да изолира и защити задачите и операционната система една от друга.

- Мащабируема микропроцесорна архитектура - концепцията предполага прозорци.

- Единицата за извличане предоставя извикване на обект в рамките на сегмент от.

- Физически адрес. Действителният капацитет на RAM и ROM паметта в компютъра се нарича физическа памет.

- Единицата за сегментиране и страниране е единица за управление на паметта.

Блокове RISC

RISC е съкращение от Reduced Instruction Set Computer (компютър с редуциран набор от инструкции) и представлява вид архитектурна стратегия за проектиране на процесори. Архитектурата на RISC микропроцесора се отнася до начина, по който е планиран и сглобен процесорът, и може да се отнася както до хардуера, така и до софтуера, който е най-близо до силиция, върху който работи. Архитектурата на набора от инструкции (ISA) определя основния софтуер.

Хардуерната архитектура на компютъра изисква код, който разделя инструкциите на 0 и 1 и който компютърът може да разбере, известен също като машинен код. Архитектурата на процесора може да бъде доста различна и софтуерът на ISA ще отрази това. Разликата между тях се състои в начина, по който се обработват задачи като работа с регистри, прекъсвания, адресиране на паметта, външни входове и изходи.

С други думи, машинният код за единия няма да работи за другия. Например, десктопът Версия за Windows няма да работи на смартфон, защото архитектурата е различна. Въпреки че Microsoft насърчава възможното свързване на за настолни компютри компютри, лаптопи и таблети след въвеждането на Windows 8.

Съществуват няколко вида процесорни архитектури и съответните ISA. Някои примери за RISC са ARM, MIPS, SPARC и PowerPC. Съвременните процесори са силно интегрирани и по-бързи, така че наборите от инструкции RISC стават все по-сложни, за да се възползват от предимствата на усъвършенстваната технология.

Архитектура CISC

За да да отговорите на въпроса какво се има предвид под CISC микропроцесорна архитектура, разгледайте CISC подхода към броя на изпълнимите инструкции. Основната му грижа в тази област е да сведе до минимум пространството за една програма, за сметка на броя на циклите. Компютрите, базирани на архитектурата CISC, са проектирани така, че да намаляват разходите за памет. Големите програми се нуждаят от повече памет, което увеличава разходите. За да се решат тези проблеми, броят на инструкциите за една програма може да се намали чрез вграждане на множество операции в една инструкция, което я прави по-сложна.

MUL зарежда две стойности от паметта в отделни регистри в CISC. Микропроцесорът използва минималния възможен брой инструкции при реализиране на хардуера и извършва операции.

Основните ключови думи, използвани в горната архитектура:

- Набор от инструкции - група от инструкции за изпълнение на програма, която управлява компютъра чрез манипулиране на данни. Форма: код на операцията (opcode) и операнд. Операнд е инструкция, която се използва за зареждане и съхраняване на данни. операндът е регистър на паметта.

- Режимите на адресиране са начинът, по който се осъществява достъпът до данните. В зависимост от вида на прилаганата инструкция режимите на адресиране биват различни, като например директен режим, при който се осъществява директен достъп до данни, или индиректен режим, при който се осъществява достъп до места с данни.

- Производителността на процесора се определя от основния закон и зависи от броя на инструкциите, CPI (цикли на инструкция) и времето на тактовия цикъл.

Предимства и недостатъци

Според форматите на използваните инструкции можем да разграничим основните типове от класификацията на микропроцесорните архитектури: RISC и CISC. Предимство на архитектурата RISC е, че тя има набор от инструкции, така че компилаторите на езици от високо ниво могат да създават по-ефективен код. Това позволява свободно използване на пространството на микропроцесорите поради простотата. Много RISC процесори използват регистри за предаване на аргументи и съхраняване на локални променливи. Функциите използват само няколко параметъра и процесорите не могат да използват инструкции за извикване, поради което използват метод с фиксирана дължина, който е лесен за превеждане.

Скоростта на работа може да бъде увеличена, а времето за изпълнение - сведено до минимум. Изисква по-малко формати на инструкциите, множество номера на инструкциите, множество режими на адресиране и добра мащабируемост. Понятието за мащабируема микропроцесорна архитектура използва регистрови прозорци, за да осигури удобен механизъм за прехвърляне на параметри между програмите и връщане на резултати. Подобен механизъм е приложен в SPARC.

Недостатъците на RISC архитектурата се дължат на факта, че в най-вече изпълнението RISC процесорите зависят от програмиста или компилатора, така че познаването на компилатора е жизненоважно при преминаване от CISC код към RISC код. Когато пренареждате CISC в RISC код, което се нарича разширяване на кода, това ще увеличи размера на. Качеството на това разширение отново ще зависи от компилатора, както и от набора от инструкции на машината. Кешът от първо ниво на RISC процесорите също е недостатък. Тези процесори имат голяма кеш памет в самия чип. Да се храни инструкции, те изискват много бързи системи за памет.

Предимството на CISC архитектурата - лесното кодиране на нови инструкции - позволи на разработчиците да направят CISC машините по-съвместими. С усъвършенстването на всеки от тях за изпълнение на задачите се използват по-малко инструкции.

Недостатъци на архитектурата CISC:

- Производителността на машината се забавя поради факта, че времето, което отнемат различните инструкции, е различно.

- Само 20 % от съществуващите инструкции се използват при типично програмиране, въпреки че в действителност има различни специализирани инструкции, които често не се използват.

- Кодовете на условията се задават от инструкциите на CISC като страничен ефект на всяка инструкция, чието задаване отнема време, и тъй като следващата инструкция променя битовете на кода на условията, компилаторът трябва да провери битовете на кода на условията, преди това да се случи.

Така че може да се обобщи, че архитектурата на набора от команди е средата, която осигурява връзката между програмиста и хардуера. Част от изпълнението и копирането на данни, изтриването или редактирането са потребителски команди за определен вид микропроцесорна архитектура.

Какво представляват уеб услугите: концепция, как работят, предимства и недостатъци

Какво представляват уеб услугите: концепция, как работят, предимства и недостатъци Какво представлява ултразвукът: видове, характеристики, диагностика, предимства и недостатъци

Какво представлява ултразвукът: видове, характеристики, диагностика, предимства и недостатъци Културна интеграция: концепция, основни моменти, предимства и недостатъци

Културна интеграция: концепция, основни моменти, предимства и недостатъци Нож за кости: видове, предимства и недостатъци. Инструкции стъпка по стъпка за направата му със собствените си ръце

Нож за кости: видове, предимства и недостатъци. Инструкции стъпка по стъпка за направата му със собствените си ръце Лепилна боя: състав, видове, предимства и недостатъци

Лепилна боя: състав, видове, предимства и недостатъци Неинхалационна анестезия: видове, класификация, предимства и недостатъци

Неинхалационна анестезия: видове, класификация, предимства и недостатъци Псевдослучайно число: методи за генериране, предимства и недостатъци

Псевдослучайно число: методи за генериране, предимства и недостатъци Прогнозиране на търсенето: концепция, видове и функции

Прогнозиране на търсенето: концепция, видове и функции Как живеят хората в япония: живот, предимства и недостатъци, характеристики

Как живеят хората в япония: живот, предимства и недостатъци, характеристики